Xilinx FPGA

StrongFirst timing solution for Xilinx® FPGAs

StrongFirst offers various oscillator products for FPGA major applications. Wired-network, medical-equipment’s, measurement, broadcast.

High-speed serial communication : Low jitter SPXO,SPSO

Broadcast, moving-picture transfer : VCXO, Programmable VCXO

Timing Synchronization IEEE1588, Sync-Ethernet : High-Stability TCXO

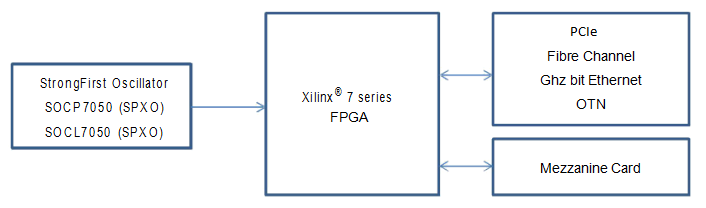

< High-speed serial communication PCIe, Fibre-Channel, OTN, G-Ethernet >

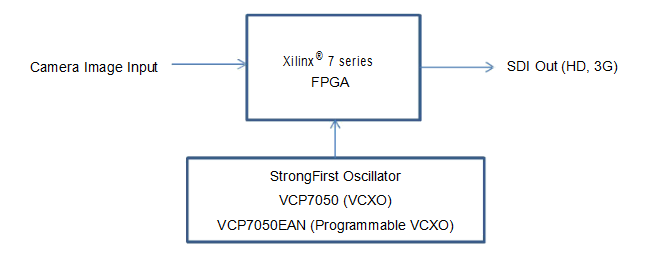

< Broadcast, moving picture transfer HD-SDI, 3G-SDI >

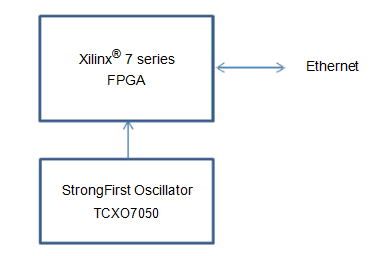

< Timing Synchronization IEEE1588, Sync-Ethernet >

Xilinx7 series FPGA transceiver block diagram

Recommended Products Line-up

Phase Jitter

(12 k to 20 MHz)

7×5×1.2t

0.23 ps Max.

(f<150 MHz)

0.23 ps Max.

(150 M≤f<200 MHz)

(Note1)

SAW based low jitter

crystal oscillator

7×5×1.6t

0.17 ps Max.

(f=100 MHz)

0.15 ps Max.

(f=156.25 MHz)

(Note2)

7×5×1.5t

0.14 ps Max.

(f=100 MHz)

0.1 ps Max.

(f=156.25 MHz)

(Note3)

Fundamental

oscillation, low

phase noise crystal

oscillator

7×5×1.6t

0.24 ps Typ.

(f=122.88 MHz)

(Note4)

High frequency

fundamental

oscillation by HFF,

low noise and low

jitter VCXO

7×5×1.5t

0.3 ps Typ.

(f=122.88 MHz)

0.26 ps Typ.

(f=153.6 MHz)

(Note5)

Low power and low

noise Programmable

VCXO by

Fractional-N PLL

StrongFirst clocks meet Xilinx® FPGA transceiver reference clock jitter requirement.

‹ Phase No ise plot and GTX/GTH/GTP(CPLL ) Mask

Recommended Reference Clock In terface

Recommended Products Line-up

Frequency

Stability

(-40 to +85 degC)

7×5×1.2t

7×5×1.2t

5×3.2×1.45t

5×3.2×1.45t

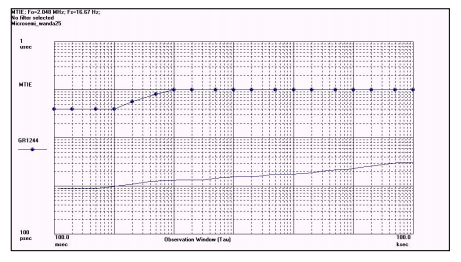

TCXO7050 24.576MHz MTIE data (0.1Hz filter)

* Xilinx is the registered trademark of Xilinx, Inc.