StrongFirst® timing solution for Altera® FP GA Stratix® V, Arria ® V, Cyclone® V Transceiver PCI Express

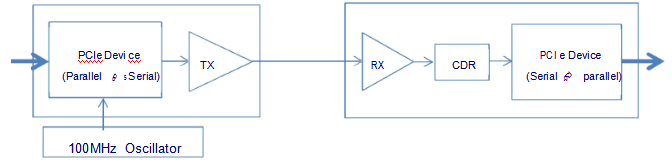

PCI Express ® (PCIe®) is a high-speed serial transmission widely adopted in PC, server, FA equipment’s, measurement equipment’s, broadcast products etc. FPGAs provide PCIe® transceivers for these applications. StrongFirst oscillators have been confirm ed as reference clock functionality by actual e valuations.

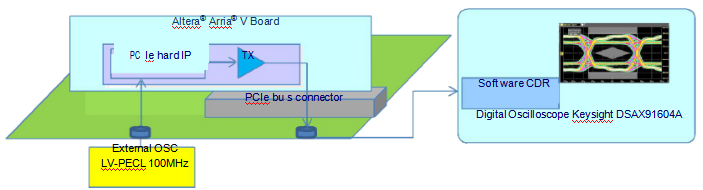

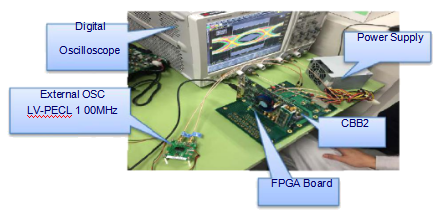

1. Connect StrongFirst oscillator to Altera Arria® V PCIe® board as reference clock.

2. Measure PCIe® TX output with oscilloscope.

3. Calculate BER with oscilloscope’s Eye Diagram and RMS data.

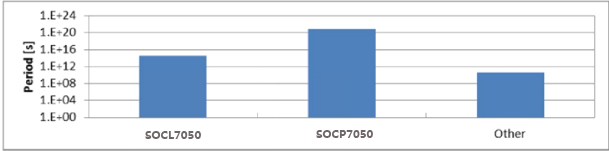

PCIe® TX oscillator measurement result, PCIe® Transmission performance

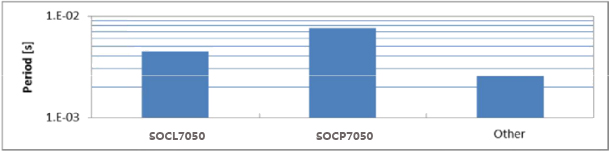

Evaluation result of 3 oscillators (SOCL7050, SOCP7050 , Other). SOCL7050 has the best performance.

BER (bit error rate )

Calculated by RMS jitter

Oscillator (100M z Reference Clock)

Other oscillator

SOCL7050

SOCP7050

PCIe G en.1 (2.5 Gb ps)

1.2 x 10-20

1.3 x 10 -27

7.5 x 10 -31 (Best)

PCIe G en.2 (5 Gb ps)

7.9 x 10-08

4.5 x 10 -08

2.6 x 10 -08 (Best)

< PCIe® Gen.1 Data speed 2.5 Gbps>

RMS and Eye Pattern

Eye Diagram Jitter

RM S (Unit : ps)

Oscillator (100M Hz reference Clock)

SOCL7050

SOCP7050

Other oscillator

(2nd PLL CDR)

5.56

4.92

6.11

BER (bit error rate) calculated with RMS.

BER (bit error rate)

Capitulated by RMS jitter

Oscillator (100M Hz reference Clock)

SOCL7050

SOCP7050

Other oscillator

(2nd PLL CDR)

1.3 x 10 -27

7.5x 10-31

1.2 x 10 -20

The timing period to the first error occasion. (Unit: sec).

< PCIe® Gen.2 Data speed 5 Gbps >

RMS and Eye Pattern

Eye Diagram Jitter

RM S (Unit : ps)

Oscillator (100M Hz reference Clock)

SOCL7050

SOCP7050

Other oscillator

(2nd PLL CDR)

5.29

5.19

5.39

BER (bit error rate) calculated with RMS.

BER (bit error rate)

Capitulated by RMS jitter

Oscillator (100M Hz reference Clock)

SOCL7050

SOCP7050

Other oscillator

(2nd PLL CDR)

4.5 x10 -08

2.6x 10-08

7.9 x 10 -08

The timing period to the first error occasion. (Unit: sec).

PCI Express, and PCIe are the registered trade marks of PCI-SIG.

Altera, Stratix, Arria, and Cyclone are the registered trade marks of Altera Corporation