RISC-V is not to be outdone! Great God Jim Keller endorsed! Enter the AI and a

2021-05-06

When many people hear RISC-V, the first thing they think of is the application of IoT and consumer electronics, as well as various low-power market opportunities. Although RISC-V has appeared in solutions such as supercomputers or data centers, or GPUs, it is often only used as an accelerator or even a "glue" under heterogeneity.

RISC-V is an architecture that has grown in popularity in recent years, and its ambitions will naturally not stop here. Recently, RISC-V has made several major moves, ready to fully enter the AI and automotive markets, and found the endorsement of the great god Jim Keller, which has once again accelerated the process of RISC-V's expansion.

Semiconductor veteran Jim Keller chooses RISC-V as the core of AI chip

Many friends who know major semiconductor manufacturers should have heard of Jim Keller, the legendary engineer. He has worked for AMD, Apple, Tesla and Intel, and participated in AMD K8, K7 and Zen, Apple A4 and A5, and special The design of chip system and architecture such as Sla HW 3.0. At the same time, he is also one of the authors of the x86-64 instruction set specification. Jim Keller's design experience can be considered to cover the two major instruction sets of RISC and CISC.

However, in June 2020, Jim Keller, who was still Intel's senior vice president at the time, submitted his resignation initiative. It is rumored that the reason for his resignation was a dispute over the plan that "the company should hand over more production to outsourcing." In January of this year, Jim Keller went to Tenstorrent, an AI chip startup, as CTO. The CEO of the company is also Jim Keller's old friend for many years, and Ljubisa Bajic, who has served as a chip architect at AMD for many years.

At the same time as this month's Linley Spring Processor Conference, Tenstorrent announced that it has obtained the authorization of SiFive's general-purpose RISC-V CPU design. The company established in 2016 will use SiFive's newly launched Intelligence X280 64-bit RISC-V core to design an SoC.

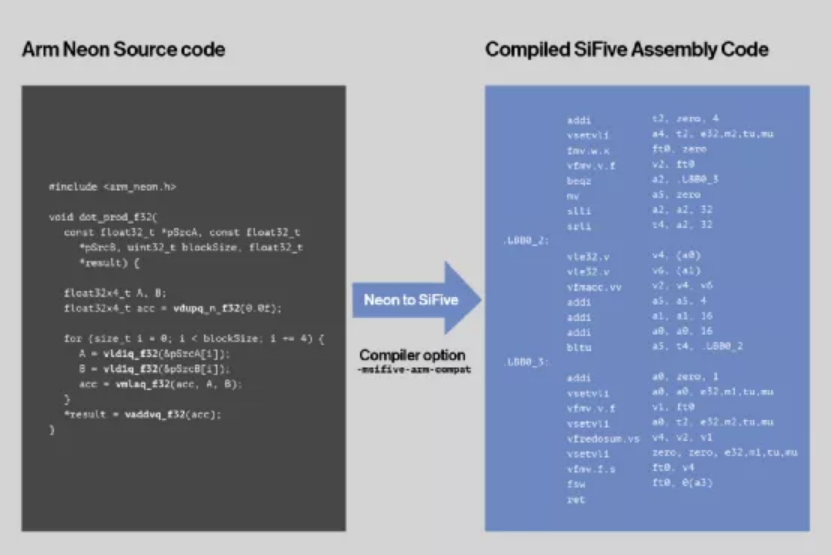

Convert Arm code to SiFive assembly code / SiFive

Intelligence is SiFive's newly launched AI/machine learning product line. It uses SiFive's AI architecture extension and RISC-V vector extension to provide software and hardware integration solutions. Intelligence X280 is based on SiFive's 64-bit U7 series RISC-V core and adopts an 8-stage pipeline design. According to data published by SiFive, Intelligence's AI extension can reduce execution time to one-twelfth, and SiFive has prepared tools for engineers to directly compile Arm Neon-based code into SiFive assembly code.

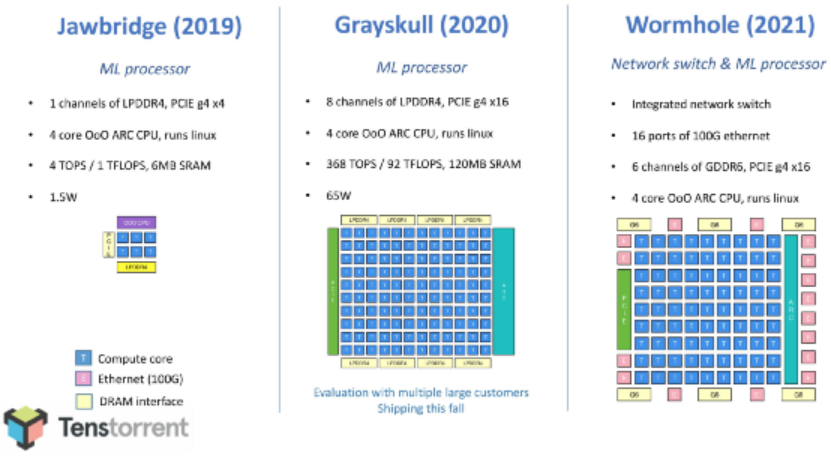

Tenstorrent machine learning processor roadmap / Tenstorrent

Tenstorrent has begun mass production of the second-generation machine learning processor Grayskull this year. The processor uses another RISC architecture ARC CPU core. Tenstorrent named it Tensix, and the process used is GLOBALFOUNDRIES's 12nm. And this selection of RISC-V core must be a decision made by Jim Keller after joining.

In an interview with foreign media HPCwire this year, Jim Keller mentioned that although many start-up companies have begun to develop and design AI chips, he has also discovered their distress in communicating with customers. One of them is the supporting software. The primary goal of many AI chip companies is to launch chips with large computing power now, using how many GFLOPS or TFLOPS as the selling point, and then design the software. Tenstorrent has paralleled software and hardware design from the beginning, and their software team has also assembled members from various compilers and CAD tools backgrounds such as Altera.

Although Tenstorrent did not disclose the specific parameters of the third-generation processor Wormhole and the fourth-generation processor under design, it is clear that RISC-V's general processing, vector processing capabilities and software ecology are what Tenstorrent values. The new Tenstorrent processor will also adopt a heterogeneous design, Tensix is responsible for the main neural network work, and Intelligence X280 is used for the introduction of application code, as well as vector operations and general computing work.

RISC-V is beginning to take shape in the automotive market

Renesas and SiFive cooperate to develop RISC-V automotive chips / Renesas, SiFive

In addition to the AI market, RISC-V has also begun to target the automotive market. Renesas announced on April 22 that it will cooperate with SiFive to develop the next generation of high-end automotive RISC-V chip solutions. Renesas Electronics Senior Vice President and General Manager of Automotive Electronics Solutions Business Unit Kataoka Takeshi said: “RISC-V plays an important role in providing additional functions and more choices for new and existing customers. We are honored to cooperate with SiFive. Using the high-end RISC-V technology of SiFive, the core of automotive electronics technology we have accumulated for many years, to develop next-generation automotive semiconductor solutions."

In fact, this is not the first time that Renesas has shown interest in RISC-V. As early as October last year, Renesas announced the launch of IP cooperation with Andes Technology and chose AndesCore 32 as the RISC-V CPU core for the dedicated standard ( ASSP) products, and plans to send samples to customers in the second half of 2021. However, this pre-programmed ASSP device is mainly used to optimize motor control, voice recognition and other fields, and does not have much connection with Renesas' strong automotive business.

This time Renesas chose to develop automotive semiconductors with SiFive, which also confirmed that the current RISC-V core can already meet the high-performance requirements for automotive applications. After all, Renesas already has its own RISC instruction set architecture SuperH, but it still has to cooperate with SiFive to develop it based on RISC-V, and it must have discovered its merits.

Another difficulty in entering the automotive market lies in various stringent certifications, but there are also RISC-V security IPs that have passed the car regulatory certification first. Rambus's hardware trust IP RT-645 has passed ASIL-D certification. It is true that this IP is only used to ensure the safety of SoC in V2X communication, ADAS, ECU, and IVI. It is not the main CPU responsible for general computing. It is also an important step taken by RISC-V in the automotive market.

summary

We have seen that RISC-V has achieved good progress in several key areas, but we have to admit that this new architecture was not lucky and encountered a semiconductor supply crisis during the golden development period. Many RISC-V processor IPs have not yet used advanced processes such as 5nm, so they can only grab orders with ARM in mature processes.

Although RISC-V has the widest penetration rate in IoT applications, it does not mean that RISC-V has stalled in this field. For example, Quanzhi recently launched the application processor D1 based on the flat head Xuantie 906 RISC-V core, and the world's first RISC-V Bluetooth 5.0 and Wi-Fi 6 SoC ESP32-C6 released by Espressif. These are definitely RISC. A large market where -V currently has an advantage will also be the first RISC-V chip to appear in front of Volkswagen engineers.

In addition, more and more chip design authorities are beginning to pay attention to RISC-V and speak out for it, take Jim Keller as an example. What he fancy is not the dispute between CISC and RISC. He believes that this is the most important thing. The most important thing is the development of scalability, usability and related tool chains, and the achievements of RISC-V in these areas are also obvious to all. After all, data centers and automobiles are also markets that ARM has taken years to break through. RISC-V has taken the first step, and the next is the real test.